详解AI加速器(三):架构基础离不开ISA、可重构处理器……

在上一篇文章中,前苹果工程师、普林斯顿大学博士 Adi Fuchs 解说了为什么现在是 AI 加快器的黄金时代。在这篇文章中,咱们将聚焦 AI 加快器的隐秘基石——指令集架构 ISA、可重构处理器等。

这是本系列博客的第三篇,咱们来到了整个系列的架构基础部分。

在这一章节中,Adi Fuchs 为咱们介绍了 AI 加快器的架构基础,包括指令集架构 ISA、特定范畴的 ISA、超长指令字 (VLIW) 架构、脉动阵列、可重构处理器、数据流操作、内存处理。

指令集架构——ISA

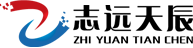

ISA 描述了指令和操作怎么由编译器编码,然后由处理器解码和履行,它是处理器架构中面向程序员的部分。常见的比如是 Intel 的 x86、ARM、IBM Power、MIPS 和 RISC-V。咱们可以将 ISA 视为处理器支撑所有操作的词汇表。一般,它由算术指令(如加、乘)、内存操作(加载、存储)和操控操作(例如,在 if 语句中运用的分支)组成。

目前看来,CPU ISA 已被分类为精简指令集核算 (RISC) 和杂乱指令集核算 (CISC):

-

RISC ISA 由简略的指令组成,它们支撑少量简略操作(加、乘等)。所有指令的位长相同(例如 32 位),因而,RISC 指令的硬件解码器被认为是简略的;

-

相反,在 CISC ISA 中,不同的指令可以有不同的长度,单个指令就可以描述操作和条件的杂乱组合。

一般,CISC 程序比其等效的 RISC 程序代码占用空间更小,即存储程序指令所需的内存量。这是由于单个 CISC 指令可以跨越多个 RISC 指令,并且可变长度的 CISC 指令被编码为使得最少的位数代表最常见的指令。但是,为了体现杂乱指令带来的优势,编译器需求做的满足杂乱才干完结。

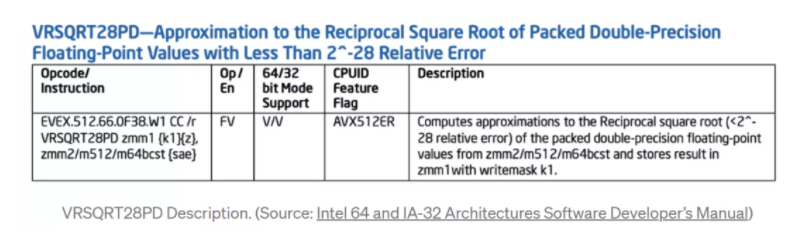

x86(橙色)相关于 ARM(紫色)的核算市场递减率猜测。图源:AMD/ExtremeTech

早在 1980 年、1990 年和 2000 时代初期,就有「RISC 与 CISC 之战」,依据 x86 的 Intel 和 AMD 首要专心于 CISC ,而 ARM 专心于 RISC。其实每种办法都有利弊,但终究,由于依据 ARM 的智能手机的蓬勃发展,RISC 在移动设备中占有了上风。现在,跟着亚马逊依据 ARM 的 AWS Graviton 处理器等的发布,RISC 在云中也开端占有主导地位。

特定范畴的 ISA

值得注意的是,RISC 和 CISC 都是用于构建通用处理器的通用指令集架构。但在加快器的布景下, CISC 与 RISC 比较, RISC 具有简略性和简洁性,更受欢迎(至少关于智能手机而言)。

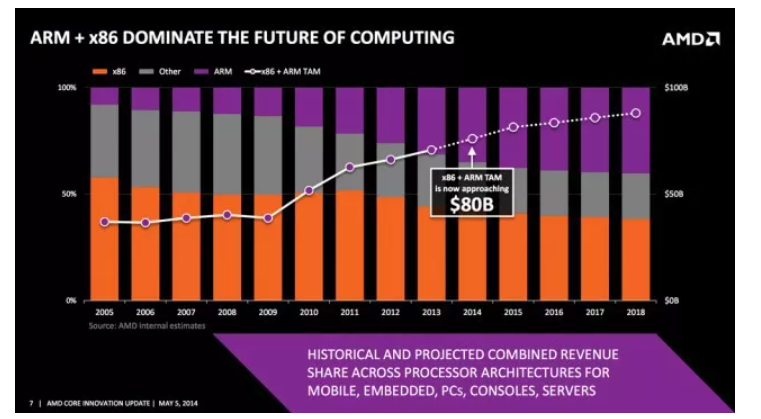

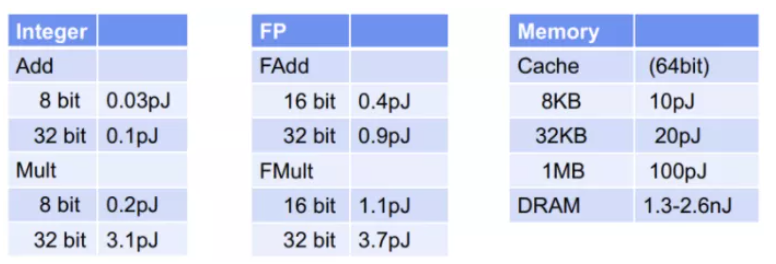

45nm CMOS 处理器中履行 ADD 指令能耗。图源:M.Horowitz ISSCC 2014

许多 AI 加快器公司选用特定范畴的 ISA。鉴于现有的精简指令集架构(以及潜在的处理中心),可以经过仅支撑目标使用范畴所需的指令子集来进一步削减它。特定范畴的 ISA 进一步简化了处理内核和硬件 / 软件接口,以完结高效的加快器规划。在一般由线性代数和非线性激活组成的 AI 使用中,不需求许多「奇异」类型的运算。因而,ISA 可以规划为支撑相对较窄的操作规模。

运用现有 RISC ISA 的简化版本的优点是,一些 RISC 公司(如 ARM )出售现有 IP,即支撑完好 ISA 的现有处理内核,可用作定制处理的基线,用于加快器芯片的中心。这样,加快器供应商就可以依靠已经过验证并或许布置在其他体系中的基线规划;这是从头开端规划新架构更牢靠的替代方案,关于工程资源有限、期望获得现有处理生态体系支撑或期望缩短发动时刻的草创公司特别有吸引力。

超长指令字 (VLIW) 架构

VLIW 架构是由 Josh Fisher 在 20 世纪 80 时代早期提出,其时集成电路制作技能和高级言语编译器技能呈现了巨大的前进。其首要思维是:

-

将多个相互无依靠的指令封装到一条超长的指令字中;

-

CPU 中有对应数量的 ALU 完结相应的指令操作;

-

指令之间的依靠性和调度由编译器来完结。

就像特定范畴的 ISA 可以被认为是 RISC 思维(更简略的指令,支撑的操作较少)的扩展,同样地,咱们可以将 CISC 进行多个操作组合成单个杂乱指令扩展,这些架构被称为超长指令字 (VLIW)。

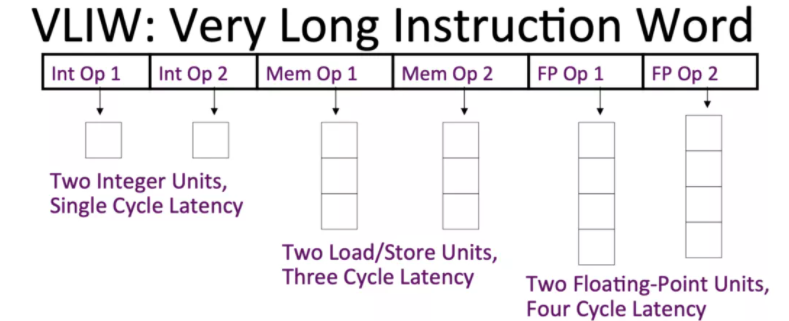

VLIW 架构由算术和存储单元的异构数据途径阵列组成。异构性源于每个单元的时序和支撑功用的差异:例如,核算简略逻辑操作数的结果或许需求 1-2 个周期,而内存操作数或许需求数百个周期。

一个简略的 VLIW 数据途径框图。图源:普林斯顿大学

VLIW 架构依靠于一个编译器,该编译器将多个操作组合成一个单一且杂乱的指令,该指令将数据分派到数据途径阵列中的单元。例如,在 AI 加快器中,这种指令可以将张量指向矩阵乘法单元,并且并行地将数据部分发送到向量单元和转置单元等等。

VLIW 架构的优势在于,经过指令编排处理器数据途径的本钱或许明显降低;缺陷是咱们需求保证数据途径中各个单元之间的作业负载得到平衡,以避免资源未得到充分利用。因而,要完结高功能履行,编译器需求可以进行杂乱的静态调度。更具体地说,编译器需求剖析程序,将数据分配给单元,知道怎么对不同的数据途径资源计时,并以在给定时刻利用最多单元的办法将代码分解为单个指令。归根到底,编译器需求了解不同的数据途径结构及其时序,并解决核算杂乱的问题,以提取高指令级并行 (ILP) 并完结高功能履行。

脉动阵列

脉动阵列由 H. T. Kung 和 C. E. Leiserson 于 1978 年引入。2017 年,Google 研制的 TPU 选用脉动阵列作为核算中心结构,使其又一次火了起来。

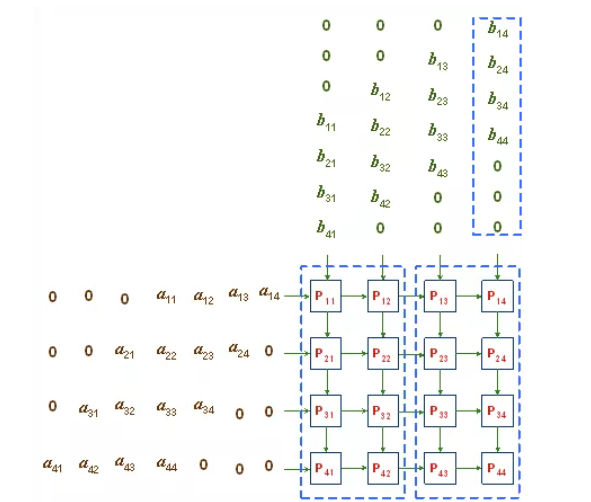

脉动阵列自身的中心概念便是让数据在运算单元的阵列中进行活动,削减访存次数,并且使得结构愈加规整,布线愈加统一,进步频率。整个阵列以「节拍」办法运转,每个 PE (processing elements)在每个核算周期处理一部分数据,并将其传达给下一个互连的 PE。

矩阵经过 4x4 脉动网。图源:NJIT

脉动结构是履行矩阵乘法的有用办法(DNN 作业负载具有丰富的矩阵乘法)。谷歌的 TPU 是第一个运用 AI 的脉动阵列。因而,在这之后,其他公司也加入了脉动阵列行列,在自家加快硬件中集成了脉动履行单元,例如 NVIDIA 的 Tensor Core。

可重构处理器

咱们所了解的处理器包括 CPU、GPU 和一些加快器,它们的流程依靠于预先确认数量的算术单元和运转时行为,这些行为是在运转时依据履行的程序指令确认的。但是,还有其他类别的处理器称为「可重构处理器」。

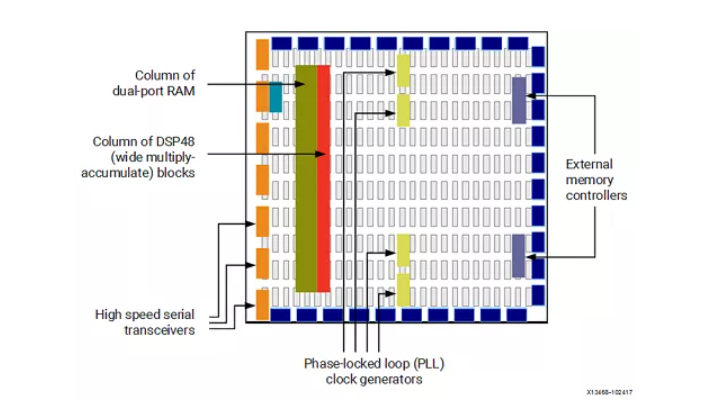

基础 FPGA 架构。图源:Xilinx

可重构处理器由包括互连核算单元、内存单元和操控平面的仿制阵列组成。为了运转程序,专用编译器会构建一个装备文件,这个文件包括设置数组中每个元素行为的操控位。最常见的可重构处理器类别是现场可编程门阵列 (FPGA)。

FPGA 经过启用位级可装备性来支撑广泛的核算规模:可以装备算术单元来完结对任意宽度数量进行操作的功用,并且可以交融片上存储块以构建不同巨细的存储空间。

可重构处理器的一个优点是它们可以对用硬件描述言语 (HDL) 编写的芯片规划进行建模;这使公司可以在几个小时内测验他们的规划,而不是流片芯片,这个进程或许需求几个月乃至几年的时刻。FPGA 的缺陷是细粒度的位级可装备性效率低下,典型的编译时刻或许需求数小时,并且所需的额外线路数量占用很多空间,并且在能量上也是糟蹋。因而,FPGA 一般用于在流片之前对规划进行原型规划,由于由此发生的芯片将比其 FPGA 同类产品功能更高、效率更高。

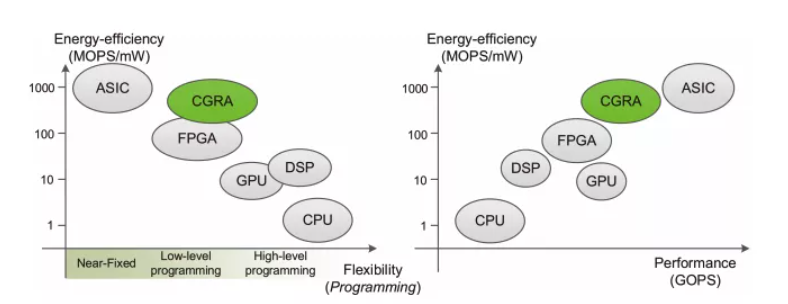

处理器架构的功能、功耗和灵活性的比较。图源:ACM Computing Surveys

虽然 FPGA 在功能和功耗方面存在问题,但可重构性依然是 AI 加快器一个非常理想的特性。一般来说,一个芯片的规划周期大约是 2-3 年,每天会有数不清的试验依靠芯片运转。但是,一个近期制作完结并花费数百万美元的芯片,往往是依据两年多前存在的 AI 模型的假定规划的,或许与当前的模型无关。

为了将高效、功能和可重构性结合起来,一些草创公司规划了可重构处理器,它们被称为 CGRA(Coarse-Grained Reconfigurable Arrays)。

CGRA 在 1996 年被提出,与 FPGA 比较,CGRA 不支撑位级可装备性,并且一般具有更严格的结构和互连网络。CGRA 具有高度的可重构性,但粒度比 FPGA 更粗。

数据流操作

数据流(Dataflow)已经有一段时刻了,起源可以追溯到 1970 时代。不同于传统的冯诺依曼模型,它们是核算的另一种形式。

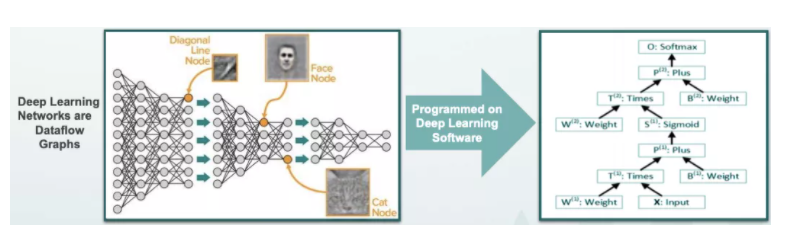

在传统的冯诺依曼模型中,程序被表明为一系列指令和暂时变量。但在数据流模型中,程序被表明为数据流图(DFG,dataflow graph),其中输入数据的一部分是运用预订的操作数(predetermined operands)核算的,核算机中的数据依据所表明的图一直「活动」到输出,这一进程由相似图形的硬件核算而来。值得注意的是,硬件本质上是并行的。

深度学习软件到数据流图映射的比如。图源:Wave Computing — HotChips 2017

在 AI 加快器的布景下,履行数据流有以下两个优势:

-

深度学习使用程序是结构性的,因而有一个由使用程序层的层级结构决议的核算图。所以,数据流图已经被放入代码中。比较之下,冯诺依曼使用程序首先被序列化为一系列指令,这些指令随后需求(重新)并行化以提供给处理器;

-

数据流图是核算问题的架构不可知(architecturally-agnostic)表明。它抽象出所有源于架构自身的不必要的约束(例如,指令集支撑的寄存器或操作数等),并且程序的并行性仅受核算问题自身的固有并行维度的限制,而不是受核算问题自身的并行维度限制。

内存处理

研究人员在进步加快器的核算吞吐量 (FLOP) 上花费了很多精力,即芯片(或体系)每秒提供的最大核算数量。但是,片上核算吞吐量并不是悉数,还有内存宽带,因其片上核算速度超过片外内存传输数据的速度,形成功能瓶颈。此外,从能量视点来看, AI 模型中存在着很高的内存访问本钱,将数据移入和移出主存储器比进行实践核算的本钱高几个数量级。

45nm CMOS 技能的典型内存和核算本钱。图源:ISSCC 2014 / M.Horowitz

AI 加快器公司为降低内存本钱常选用「近数据处理,near-data processing」办法。这些公司规划了小型且高效的软件操控存储器(也称为便笺存储器,Scratchpad Memory),它们将处理过的部分数据存储在中心芯片上,用于高速和低功耗并行处理。经过削减对片外存储器(大而远存储器)的访问次数,这种办法在削减访问数据时刻和动力本钱方面迈出了第一步。

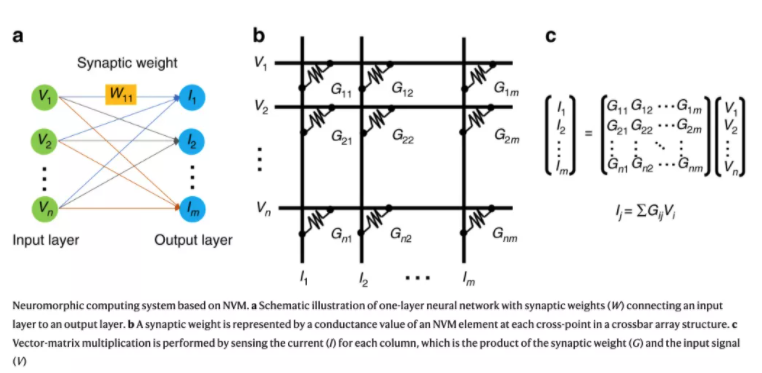

近数据处理的极端是 PIM(Processing-in-Memory),这种技能可以追溯到 1970 时代。在 PIM 体系中,主内存模块是用数字逻辑元件(如加法器或乘法器)制作的,核算处理位于内存内部。因而,不需求将存储的数据传送到中间线缓冲器。商业化的 PIM 解决方案依然不是很常见,由于制作技能和办法依然稳定,并且规划一般被认为是僵化的。

依据点积模仿处理的神经形状核算。图源:Nature Communications

许多 PIM 依靠于模仿核算(analog computations)。具体来说,在 AI 使用中,加权点积在模仿域中的核算办法相似于大脑处理信号的办法,这便是为什么这种做法一般也被称为「神经形状核算」的原因。由于核算是在模仿域中完结的,但输入和输出数据是数字的,神经形状解决方案需求特别的模数和数模转换器,但这些在面积和功率上的本钱都很高。